- Structural Optimization for Next-Generation Devices

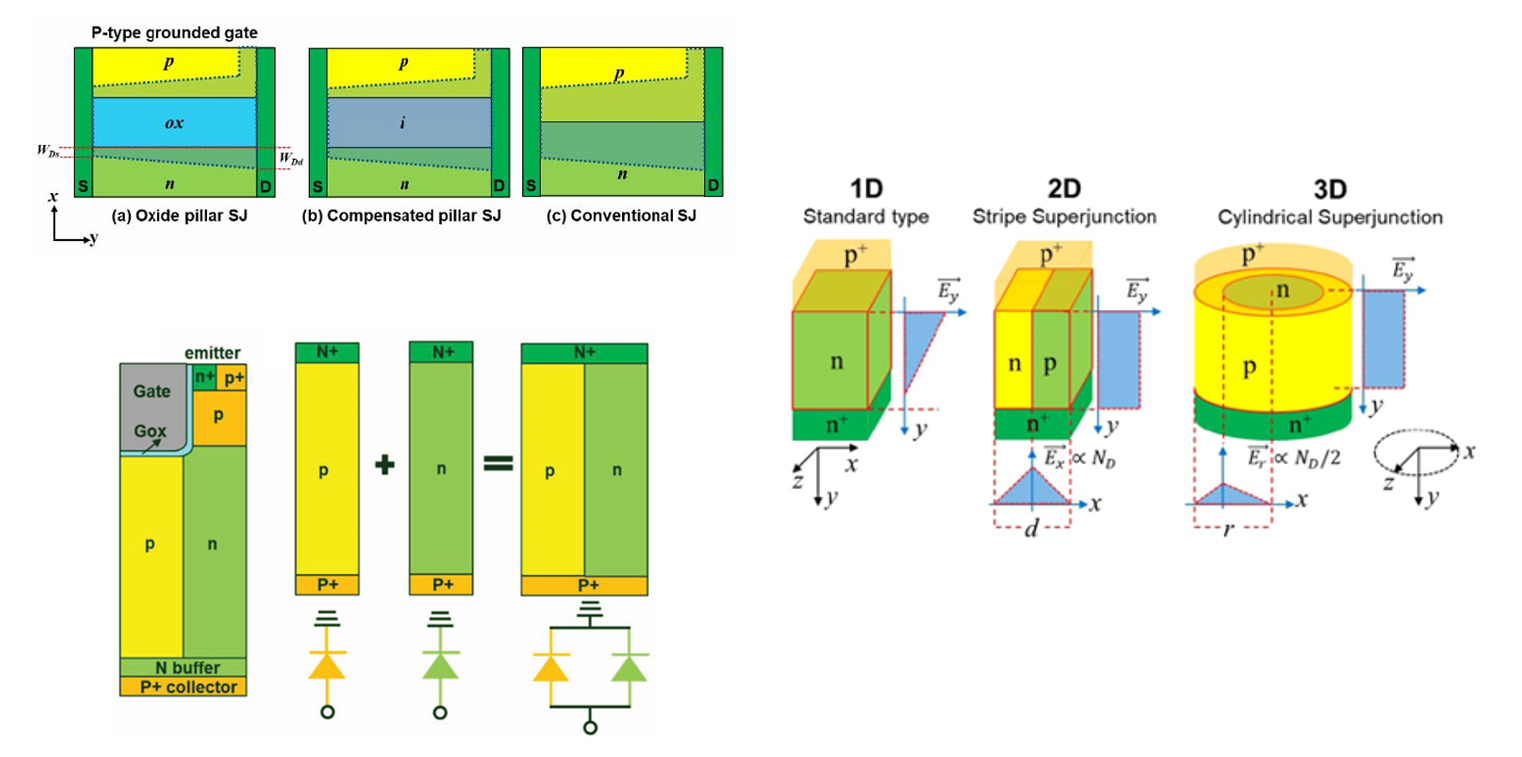

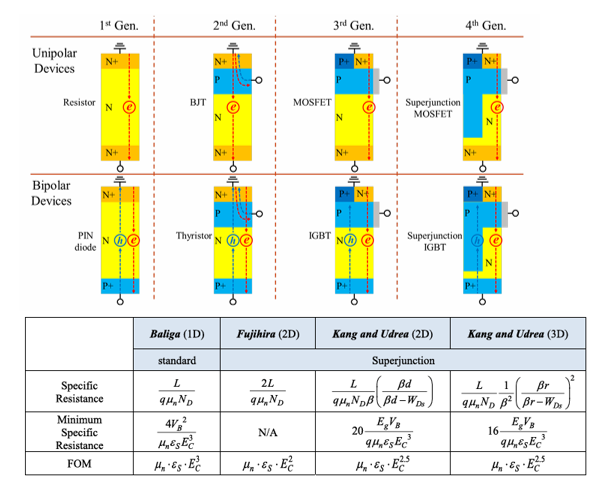

We explore novel device architectures designed to overcome the inherent trade-offs of conventional structures. By introducing advanced structural concepts—such as optimizing pillar geometries and incorporating dielectric materials—we minimize parasitic effects and maximize the performance figure of merit, achieving a superior balance between breakdown voltage and on-state resistance.

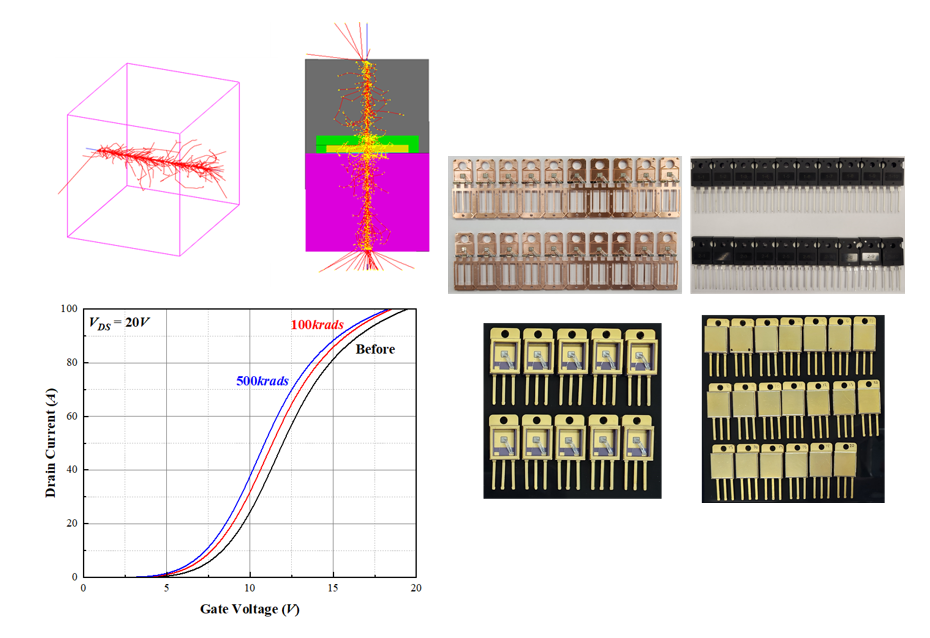

Moving beyond traditional planar and 2D limitations, we investigate device architectures across multiple dimensions. By analyzing electric field distributions in 3D space, we design structures that enhance the depletion region and allow for higher doping concentrations, thereby significantly reducing on-state resistance.